The announcement of the ZEN 6 -architecture of AMD, which received the codename “Medusa”, caused lively discussions in the IT community. It turned out that important changes in the memory controller can influence the work of processors in combination with some existing motherboards of the AM5 platform.

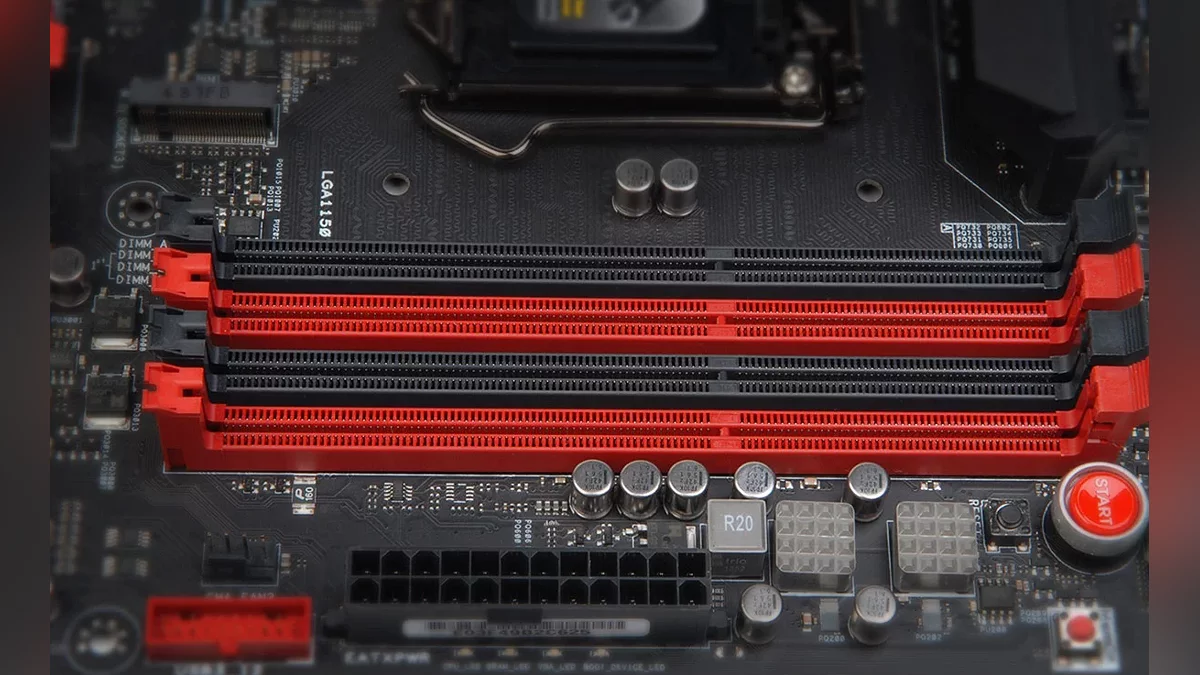

According to sources, the Zen 6 processors receive two independent memory controllers (IMC), for which an assessment of DIMM -Slots configuration is required. In contrast to current solutions, where A0 and B0 channels are used, the new chips are optimized for slots A1 and B1. This is due to the characteristics of the DDR5 topology, which is designed in Zen 6 to communicate with one RAM module on the channel.

As a result, boards with two DIMM slots can encounter limitations in mini-itx or micratx formats. When using A0/B0 slots, Zen 6 processors, for example, cannot disclose the indicated performance. In addition, part of the functionality, including support for high -frequency memory, can be inaccessible.

Interestingly, AMD does not exclude software adjustment to work with current councils, but this will lead to a decrease in data processing speed. Manufacturers have already started the production of compatible solutions -for example, MSI introduced the MPOWER model with A1/B1 configuration, previously characteristic of very specialized boards.

Experts note that Zen 6 will be the first significant step in the evolution of AM5: in addition to changes in the memorial sub -system, an increase in the number of boxes and the volume of the cache in top models is expected. Users who plan an upgrade, however, must take into account the nuances of compatibility to prevent an unexpected decrease in performance.

👨️ Hyip schedule 1 is accused of plagiarism

Source: VG Times

Gregory Robert is a sports aficionado and a writer for “Social Bites”. He provides in-depth coverage of the latest sporting events and trends, offering a unique and knowledgeable perspective on the world of sports.